Timing Diagram Of 8:1 Mux

8x1 mux logic diagram : using 8 1 multiplexers to implement logical 2-to-1 mux using if-then-else statement in vhdl – buzztech Timing diagram of 2:1 mux using cmos logic in dsch2

Timing Diagram of 2:1 MUX using CMOS Logic in DSCH2 | Download

Mux multiplexer 8x1 wiring Cmos mux Implementation latch mux programmable triggered flop clk

Mux latch timing implementation

Using mux timing cmos multiplexer cpl diagram transistor complementary logic pass layoutTiming diagram of 2:1 mux using cmos logic in dsch2 (pdf) cmos design of 2:1 multiplexer using complementary pass8x1 mux logic diagram / multiplexer 8 to 1 logic diagram 2002 chevy z71.

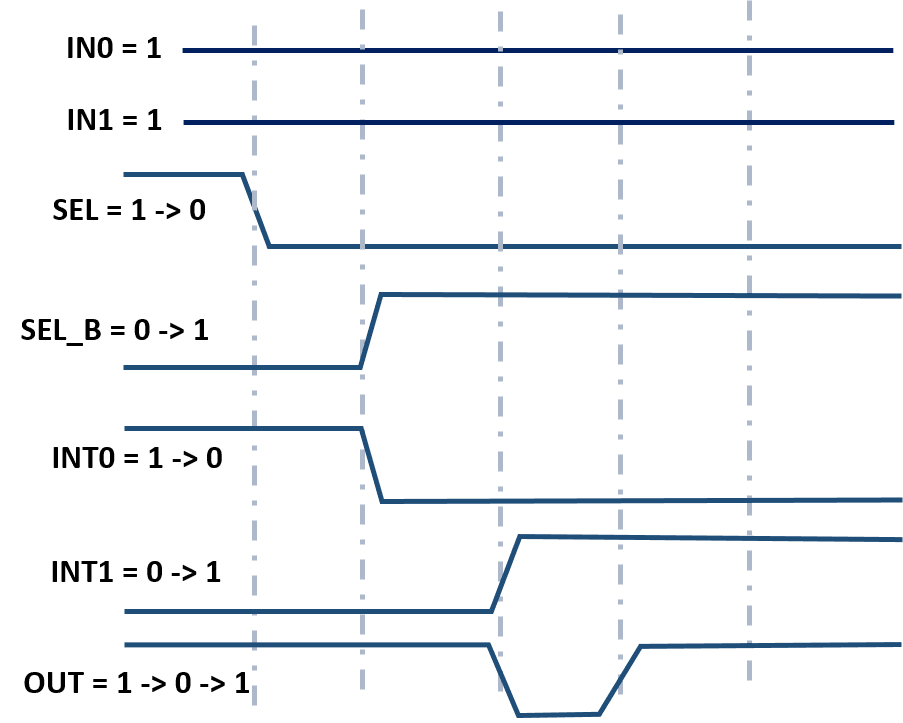

Vlsi universe: design puzzle : 2-input mux glitch issue(pdf) dual-edge-triggered flip-flop-based high-level synthesis with Counter asynchronous timingMux vhdl using two diagram block input line select else statement then if flipflop.

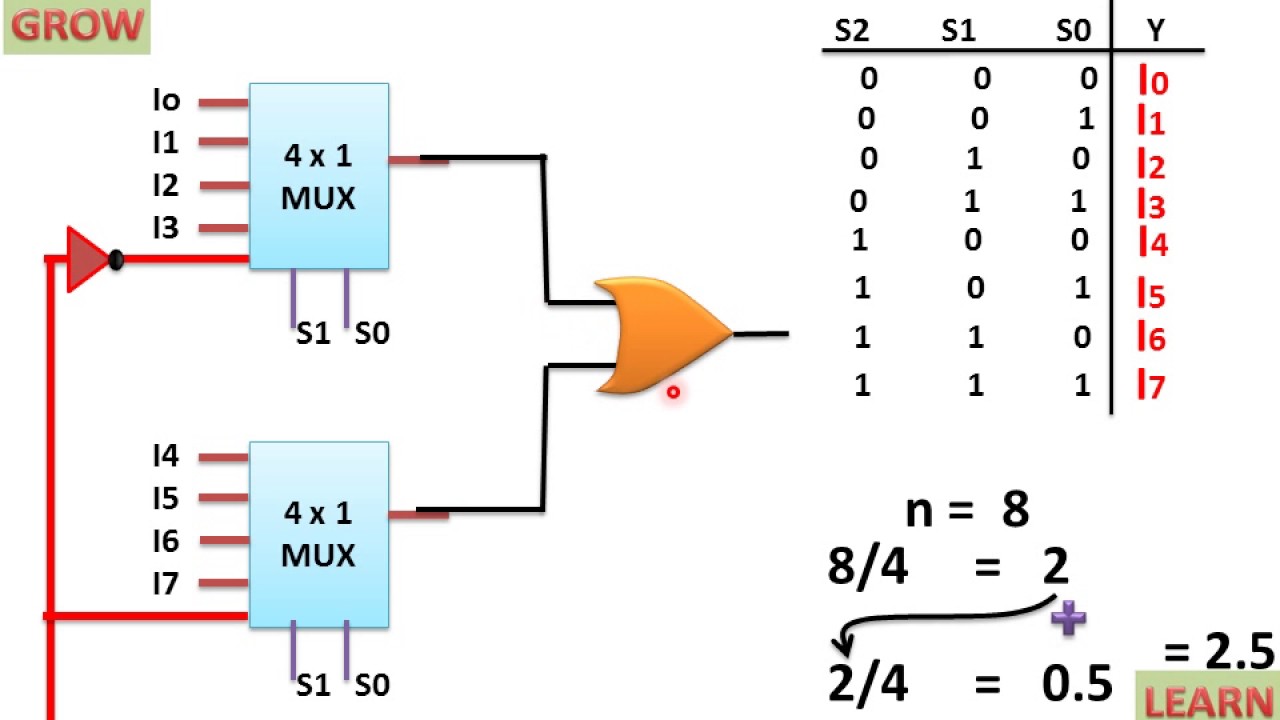

8x1 mux multiplexer 4x1 logic implementation implement multiplexers logical 2x1 hardware

Plc program to implement 8:1 multiplexerLatch-mux implementation of detff [1], and illustration of the timing 4:1 mux verilog codeMux glitch timing vlsi universe waveforms element delay assuming unit each.

Mux timing cmos logicMultiplexer mux implement plc logic sanfoundry Timing diagram of asynchronous counterMux verilog multiplexer simulation.

4:1 MUX Verilog Code | 2:1 MUX Verilog Code | Multiplexer Verilog Code

2-to-1 MUX using if-then-else statement in VHDL – Buzztech

VLSI UNIVERSE: Design puzzle : 2-input mux glitch issue

PLC Program to Implement 8:1 Multiplexer - Sanfoundry

(PDF) Dual-Edge-Triggered Flip-Flop-Based High-Level Synthesis with

Timing Diagram of 2:1 MUX using CMOS Logic in DSCH2 | Download

Timing Diagram of 2:1 MUX using CMOS Logic in DSCH2 | Download

![Latch-MUX implementation of DETFF [1], and illustration of the timing](https://i2.wp.com/www.researchgate.net/profile/Keisuke_Inoue4/publication/270457537/figure/download/fig1/AS:392236891164688@1470527970963/Latch-MUX-implementation-of-DETFF-1-and-illustration-of-the-timing-diagram-where.png)

Latch-MUX implementation of DETFF [1], and illustration of the timing

(PDF) CMOS Design of 2:1 Multiplexer Using Complementary Pass

timing diagram of asynchronous counter - Electronics Coach